TimingTutorial

Flowgraph Timing - a brief tutorial

Rough draft - Work in Progress

What determines the timing for a flowgraph

There are several factors which determine the rate at which data flows from one block to the next. However, many beginners assume that if, for example, a waveform source is set to a certain frequency, and a sample rate is set, then that output signal will be at that rate. But as opposed to a hardware circuit, the signal is just data in a buffer. The following sections will illustrate this.

Source hardware example

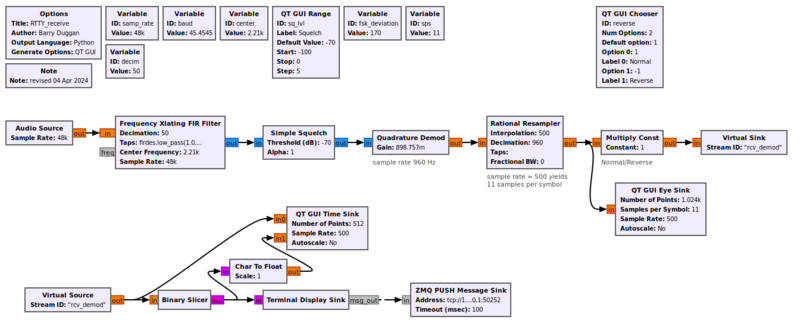

The following discussion is based on this flowgraph:

Frequency shift keying (FSK) tones are input to the microphone jack of the computer which has a sample rate of 48khz. That data is fed to a Frequency Xlating FIR Filter which shifts the tones above and below the center frequency. It also decimates (divides) the sample rate by 50, producing an output sample rate of 960.

The Quadrature Demod produces a signal which is positive or negative depending on whether the tone is above or below the center frequency.

The Rational Resampler interpolates (multiplies) the sample rate by 500 and decimates it by 960 to produce an output sample rate of 500. For the RTTY rate of 45.4545 baud (the exact definition is 1/0.022), this produces exactly 11 samples per bit time.

The 'Terminal Display Sink' is an Embedded Python Block which reads the input stream of 1's and 0's, synchronizes on the start bit, uses a majority of samples in a bit to determine validity, creates a Baudot character from the five data bits, converts Baudot to UTF-8, and displays the characters on the user terminal screen.

Sink hardware example

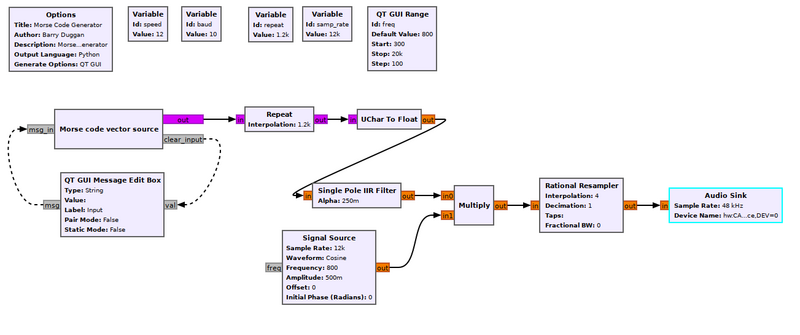

The following discussion is based on this flowgraph: